在 IEDM 2023 上,Naoto Horiguchi 介绍了 CFET 和中段集成。我有机会与 Naoto 讨论这项工作,这篇文章是基于他在 IEDM 上的演讲以及我们的后续讨论。我一直很喜欢与 Naoto 交谈,他是逻辑技术开发领域的领导者之一,以易于理解的方式解释技术,反应灵敏且易于合作。

为什么我们需要 CFET?

由于 CMOS 缩放已从纯粹基于间距的缩放过渡到基于间距加轨道的缩放,因此必须减少鳍片数量,请参见图 1。每次减少鳍片数量,性能都会降低。

图 1. 标准单元缩放

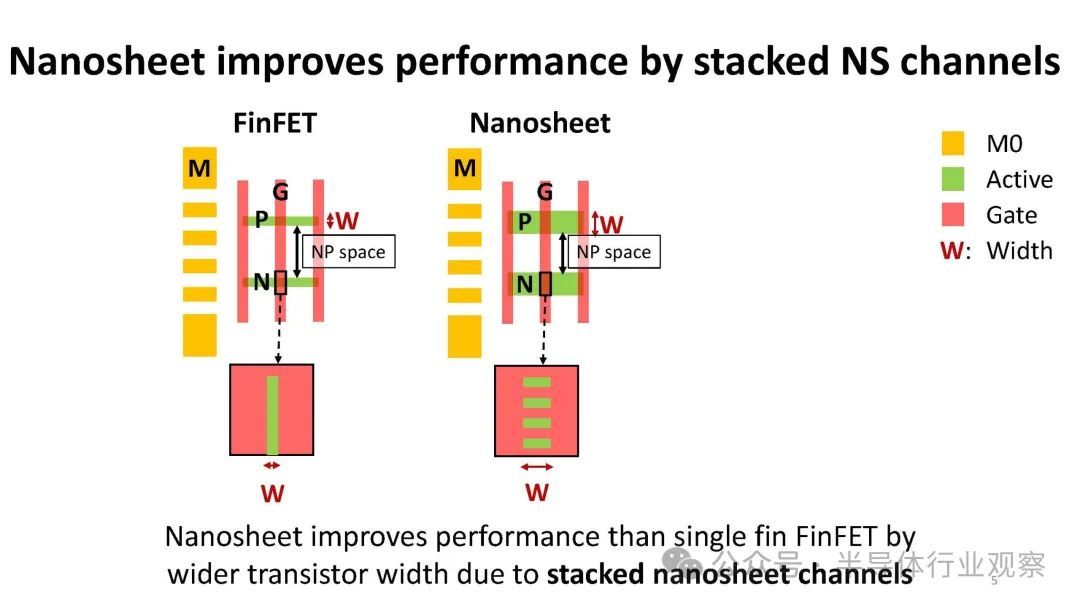

通过从 FinFEt 转向堆叠水平纳米片 (HNS:Horizontal NanoSheets),可以通过更宽的纳米片堆叠和垂直堆叠多个纳米片来改善/恢复性能,见图 2。

图 2. Nanosheet 优势

但正如我们所见,FinFET 纳米片缩放最终会导致性能下降,见图 3。

图 3. 纳米片缩放限制

CFET(互补 FET)将 nFET 和 pFET 堆叠起来,见图 4。

图 4.CFET

CFET 再次重置了缩放限制,因为 nFET 和 pFET 堆叠在一起,并且器件之间的 np 间距变为垂直而不是水平,这使得片材更宽,见图 5。

图 5. CFET 改进的缩放比例

图 6 比较了 HNS 和 CFET 性能与单元高度的关系,突出显示了 CFET 的优势。

图 6. HNS 与 CFET 性能与单元高度

单片 CFET 与顺序 CFET

CFET 制造有两种根本不同的方法。在单片流程中,CFET 以连续工艺流程在晶圆上制造。在顺序流程中,在一个晶圆上制造底部器件,然后将第二个晶圆接合到第一个晶圆上,并在第二个晶圆上制造顶部器件。

在顺序流程中,两个器件之间存在键合电介质,见图 7。

图 7. 单片 CFET 与串行 CFET

由于键合电介质的存在,该结构更高,并且具有更高的电容衰减性能,见图 8。

图 8. 单片/串行 CFET 性能比较

顺序 CFET 的制造成本比单片 CFET 更昂贵,而且在性能下降的情况下,业界似乎将重点放在单片 CFET 上。

单片 CFET 处理

单片 CFET 工艺如图 9 所示。

图 9. 单片 CFET 工艺流程

粗体步骤特别具有挑战性:

水平纳米片堆叠(鳍片)已经具有很高的纵横比,为了制造 CFET,您需要将 nFET 和 pFET 堆叠堆叠在一起,中间有一个相对较厚的层,高度增加一倍以上;

如前一点所述,栅极形成也具有高纵横比;

外延源极/漏极必须彼此垂直隔离;

没有明确指出,制造底部器件源极/漏极,然后制造顶部器件顶部源极/漏极。顶部器件的热处理和后续步骤必须在足够低的温度下完成,以免降低底部器件的性能;

本次演示中一个特别有趣的部分是中间介电隔离 (MDI) 部分,我以前从未见过这个问题。MDI 证明了内部垫片和功函数材料 (WFM) 图案化.

图 10 说明了 MDI 对内部隔离物形成(左侧)和 WFM 图案化(右侧)的影响。

图 10. 中等介电隔离影响

图 11 说明了 MDI 集成流程。

图 11. MDI 集成流程

通过集成 MDI,可以增加 nFET 和 pFET 之间的垂直间距,而不会影响内部间隔物的形成。

如前所述,制造底部器件源极/漏极,然后制造顶部器件源极/漏极。在形成底部源极/漏极之后,沉积隔离电介质并回蚀以暴露顶部器件以进行源极/漏极外延形成。隔离回蚀必须通过 MDI 高度进行控制,见图 12。

图 12. 用于垂直边缘放置对齐的 MDI

为了最大限度地减少器件性能的热退化,需要采用偶极子优先处理且无需退火和低温夹层形成工艺的新 WFM 选项,见图 13。

图 13. 低温栅极堆栈选项

还需要低温源极/漏极生长和用于接触形成的低温硅化物,见图14。

图 14. 低温源极/漏极和触点选项

低温硅化物对于背面与底部器件的直接接触尤其重要。CFET 互连需要与底部和顶部器件接触,随着背面电力传输的出现,顶部器件将从正面互连堆栈接触,而底部器件将从背面接触。钼 (Mo) 和铌 (Nb) 有望用于 pFET,钪 (Sc) 则有望用于 nFET,尽管 Sc 很难用 ALD 沉积。

背面和中部线路互连

正如我之前所写,背面供电网络 (BSPDN) 预计将于今年由英特尔、三星和台积电于 2026 年推出。将互连分为前端信号连接和背面电源连接,可减少 IR 压降(功率损耗)一个数量级,见图 15。

图 15. BSPDN 降低 IR 压降

BSPDN 还改进了轨道扩展,支持从 6 轨道单元减少到 5 轨道单元,见图 16。

图 16. BSPDN 轨道缩放

与水平堆叠纳米片 (HNS) 相比,BSPDN 与 CFET 的集成可降低 20% 至 40% 的功耗,见图 17。

图 17. 具有 BSPDN 的 CFET

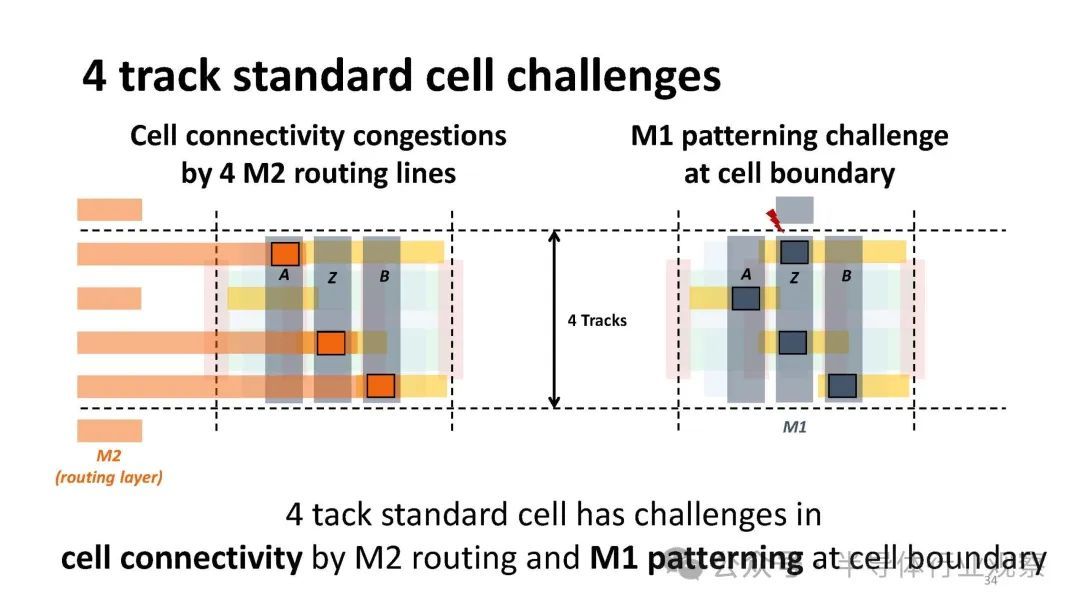

为了从 5 轨单元升级到 4 轨单元,必须克服互连挑战,见图 18。

图 18. 4 轨cell互连挑战

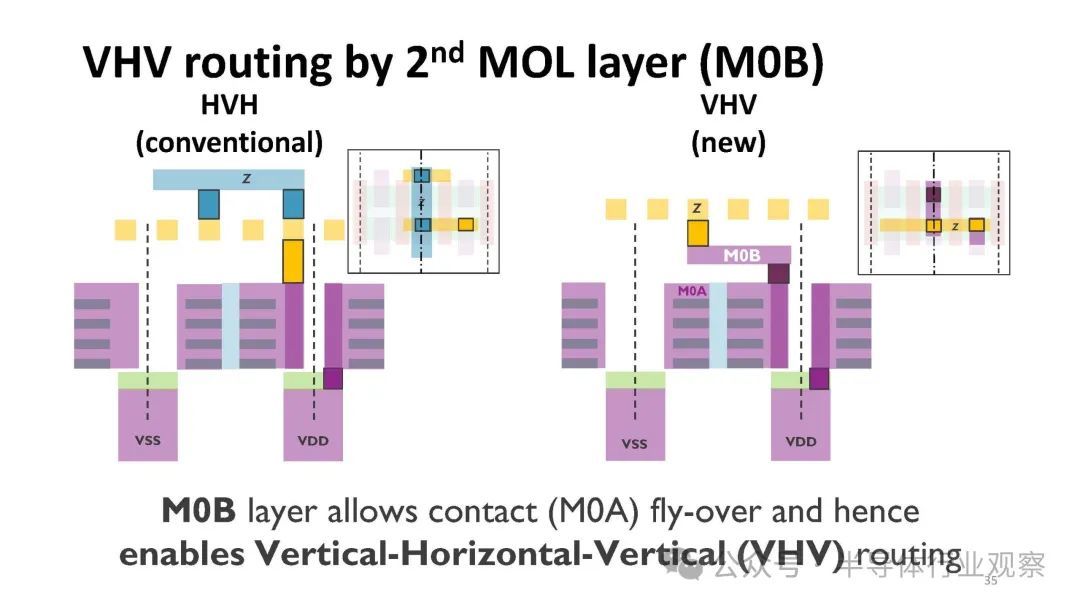

具有附加中线 (MOL) 层的垂直-水平-垂直布局可以启用 4 轨单元,见图 19。

图 19. VHV 路由和第二个 MOL 层

众所周知,逻辑设计由标准单元构建,例如反相器、与非门、扫描触发器和其他单元。标准单元的宽度是一定数量的接触多晶硅节距 (CPP),具体取决于单元类型以及单元是否具有单扩散中断或双扩散中断,例如 2 输入 NAND 门对于单扩散中断将为 3CPP 宽, 4CPP 宽,用于双扩散断裂。标准单元的高度由金属 2 节距 (M2P) 乘以轨道(M2P 数量)来表征。

由于扩展 CPP 和 M2P 变得越来越困难,设计技术协同优化 (DTCO) 在通过减少轨道等技术进行扩展时变得越来越重要。目前最小的单元一般是6轨,也出现了一些5轨单元。而Imec 则讨论了启用 4 轨单元的路由技术。

图 20. 显示了从 9 轨到 4 轨的 Imec 路线图

在介绍此处描述的布线技术之前,我想简要介绍一下单元高度缩放的其他要求,仅讨论 M2P 和轨道会忽略底层设备结构。单元高度必须适合 n 和 p FET、n 到 p 间距和边界宽度。从 FinFET 到水平纳米片 (HNS) 的转变通过从占用水平空间的多个鳍切换到垂直方向的纳米片堆叠来实现 n 和 p FET 的缩放。

Imec 正在开发forksheets (FS) 和埋入式电源轨 (BPR:buried power rails ) 等技术来解决器件高度问题,例如,BPR 可以用基板中的高薄电源轨取代宽的 metal-2 电源轨,从而减少边界宽度,和 forksheets 可以减少 n 到 p 的间距。无论采用何种特定技术,设备都必须互连。

前沿工艺已在Metal 1 层下引入了中线互连层,这些附加层在 Imec 的术语中通常称为 Metal 0 (M0) 或 Mint。为了实现 4 轨单元,单个 M0 层不足以互连设备。在这项工作中,M0A 和 M0B 添加在 Mint 下方,并且在新颖的流程架构中,Mint 被用作掩模,在 M0B 中执行尖端到尖端的切割。

Mint 通过 VintB 通孔向下连接到 M0B,并通过 VintG 连接到栅极触点。M0B 通过 V0A 向下连接至源极漏极至 M0A。

图 21 说明了 Mint 的 4 轨单元中的拥塞情况

图 22说明了 M0B 和 M0A 的添加。

为了实现所需的紧密尖端到尖端间距,M0B 使用自对准切割,其中 Mint 充当掩模,这需要减材金属化工艺。这里使用的金属化是使用半镶嵌技术沉积的钌(与铜不同,钌可以进行干蚀刻),见图23。

图 23. 半镶嵌

自对准 M0B 切割如图24所示。

图 24.M0B 自对准切割。

通过添加两层并使用自对准切割,可以互连 4 轨单元。如果底层器件结构也可以实现所需的缩放,则该互连方案提供了通向 4 轨单元和持续缩放的路径。

我问 Naoto 需要什么才能超越 4 轨单元到 3 轨单元,他回答说 Imec 现在正在研究优化,它可能需要额外的 MOL 层,并且可能需要在会影响标准单元布局的设备。

我还问 Naoto,他认为我们什么时候可能会实现 CFET,他说可能是 A10 逻辑一代或 A7 一代。

作者指出,英特尔、三星和台积电今年都在 IEDM 上发表了有关 CFET 的研究成果,并且英特尔和台积电都有技术选项图,显示 FinFET 让位于 HNS,然后是 CFET。

Imec 在作为 HNS 之后的下一代选择的 CFET 开发方面继续展现出出色的进展。在此工作中,设备集成选项以及 BSPDN 和 MOL 选项均已描述。